版图设计中的一些小tips

版图设计中的一些小tips

Via enclosure应该怎么画

以TSMC 28nm HPCPLUS为例:

常见的DRC报错为Mx.EN.2Mx.EN.3Mx.EN.14__Mx.EN.15:

相关的DRC rule列出如下:

Mx.EN.2: Enclosure of square VIAx-1 [at least two opposite sides] N $\geq$ 0.03

Mx.EN.3: Enclosure of VIAx-1 [all sides] P $\geq$ 0.02

Mx.EN.14: Enclosure of square VIAx-1 M $\geq$ 0.01

Mx.EN.15: Enclosure of square VIAx-1 [at least two opposite sides] N $\geq$ 0.025

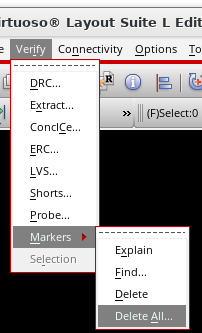

cell无法复制的问题

一般是版图中包含markers导致复制不成功,删除掉marker即可。

VIVA Graph测量pulse width快捷键

A: 添加sample点

D: 测量差距

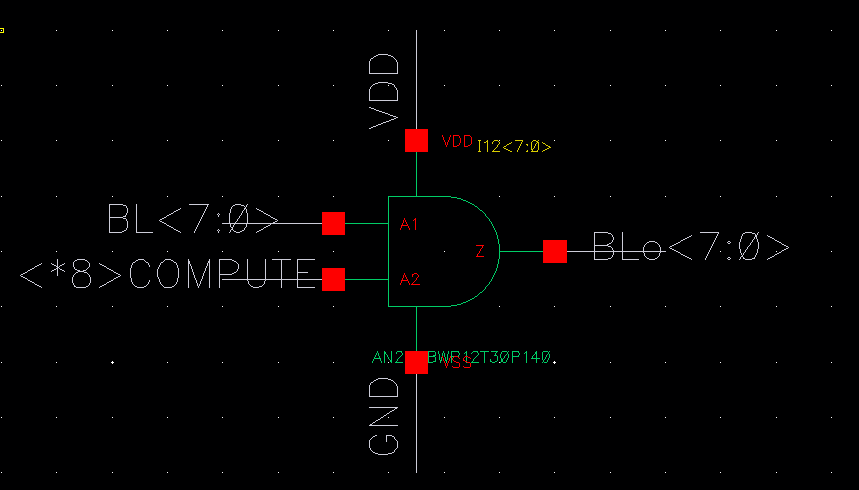

schematics中生成多个instance

示例:

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 _ConchNest🐚!