ASIC实现一个简单数字模块的流程

ASIC实现一个简单数字模块的流程

数字模块功耗分析

primetime报告toggle rate的命令:1

report_switching_activity -average_activity -hierarchy -based_clock $clk_name

innovus后端

在PR文件夹下创建以下子文件夹,并将default.view文件拷贝进来。

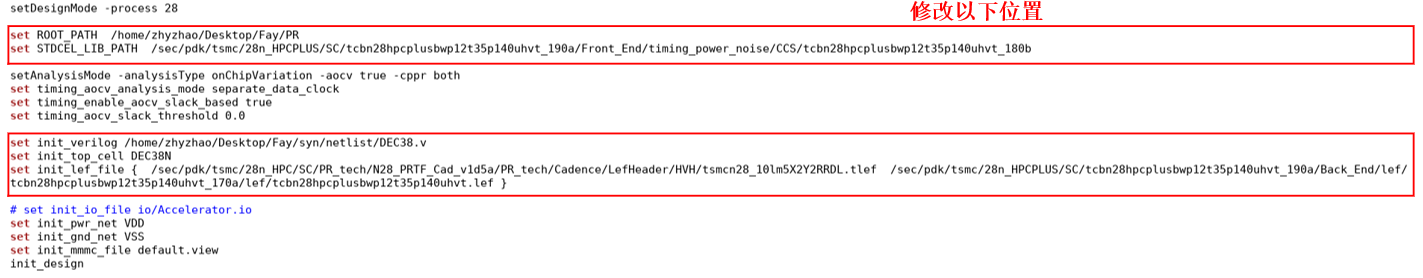

简单修改init_design.tcl中的部分。

pcell与pycell的区别

在28nm库的technology file中有pcell与pycell两个文件夹,位置在/sec/pdk/tsmc/28n_HPCPLUS_V2103/PDK/Techfile/online/1P10M_5X2Y2R下。问题是pcell与pycell的区别是什么?

答:

从高层次上讲,Pycells 是用 Python 语言编写的参数化的标准单元库,这些需要来自 Ciranova(现在是 Synopsys)的技术,并且不被 Cadence 支持。而 PCells 是用 SKILL(或面向对象的 SKILL,称为 SKILL++)编写的,并且得到 Cadence 的支持。PCells 在 Cadence 工具和工具流程中经过了充分的测试。

无论使用 Pycells 还是 SKILL Pcells,大多数代工厂的 PDKs 都会努力确保无论使用哪一种,布局都是相同的。但使用Pycells存在可能的风险,可能某些功能变得不可用(例如 modgens、placement、在 Virtuoso 内部运行的 PVS等),对于virtuoso streamin而言,建议使用pcell。

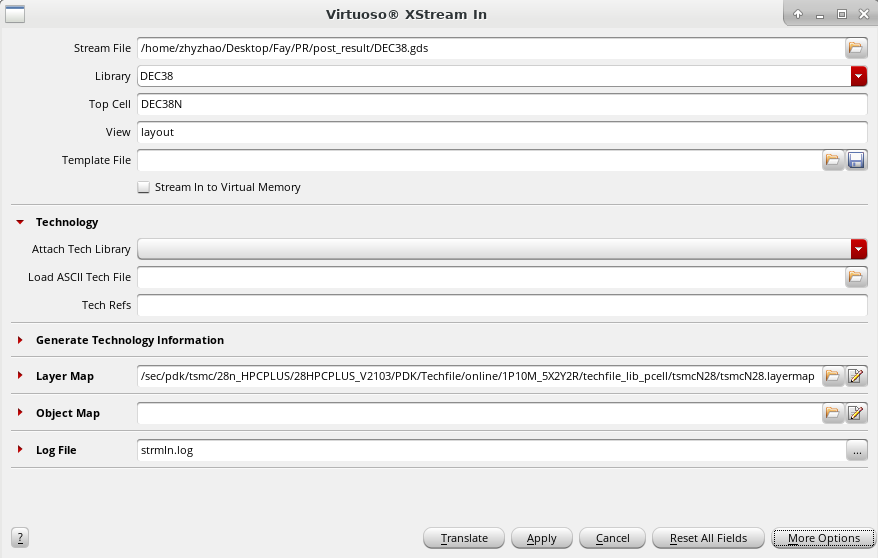

streamIn

注意以下四个点:

- 由于standard cell被merge了进来,可以选择创建一个新库,然后进行streamIn,streamIn成功后再进行verilogIn

- layermap文件的选择,一般该文件存放在/sec/pdk/tsmc/28n_HPCPLUS_V2103/PDK/Techfile/online/1P10M_5X2Y2R/pcell下。

- 在More Options中选择Replace [] With <>

- 如果pin过于密集,可以在geometry中调低scale text height。

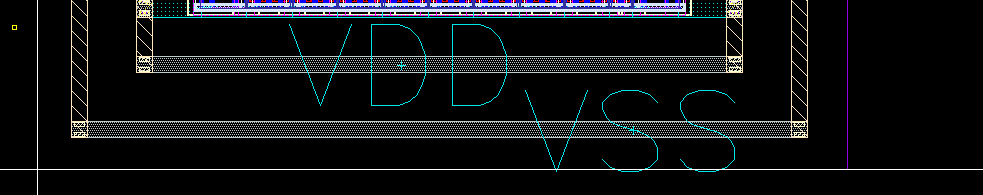

接下来在power ring上手动打上VDD与VSS的lable

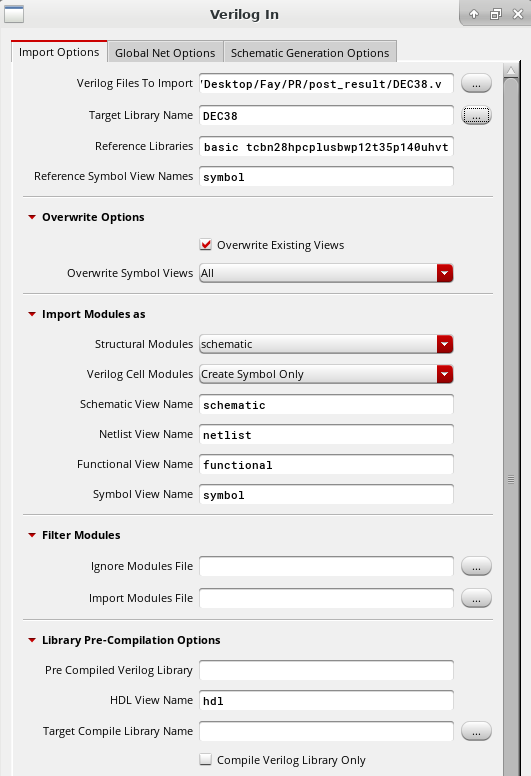

VerilogIn

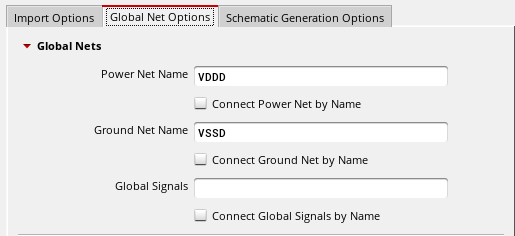

注意在Global Net Options将Power/Ground Net Name改为VDDD与VSSD,这一步是为了把VDD与VSS后的感叹号去掉。

同样,手动添加VDD与VSS的pin。

最后跑LVS,完成模块的部署。