Digital as a top流程

Digital as a top流程

编写.lib文件

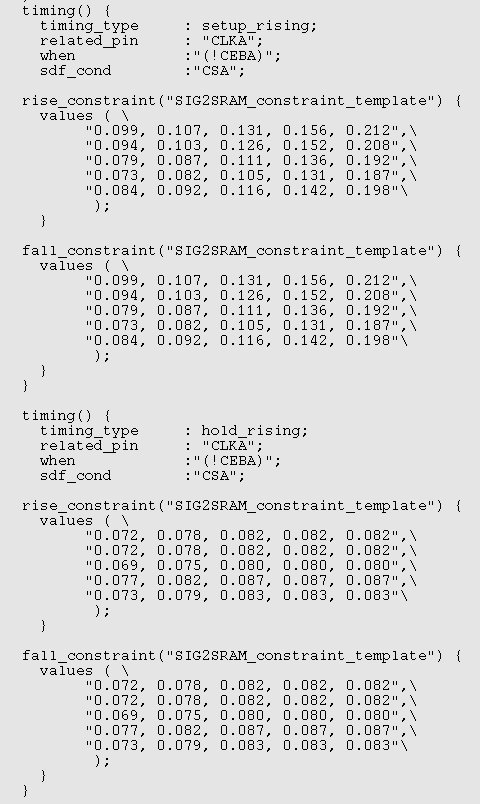

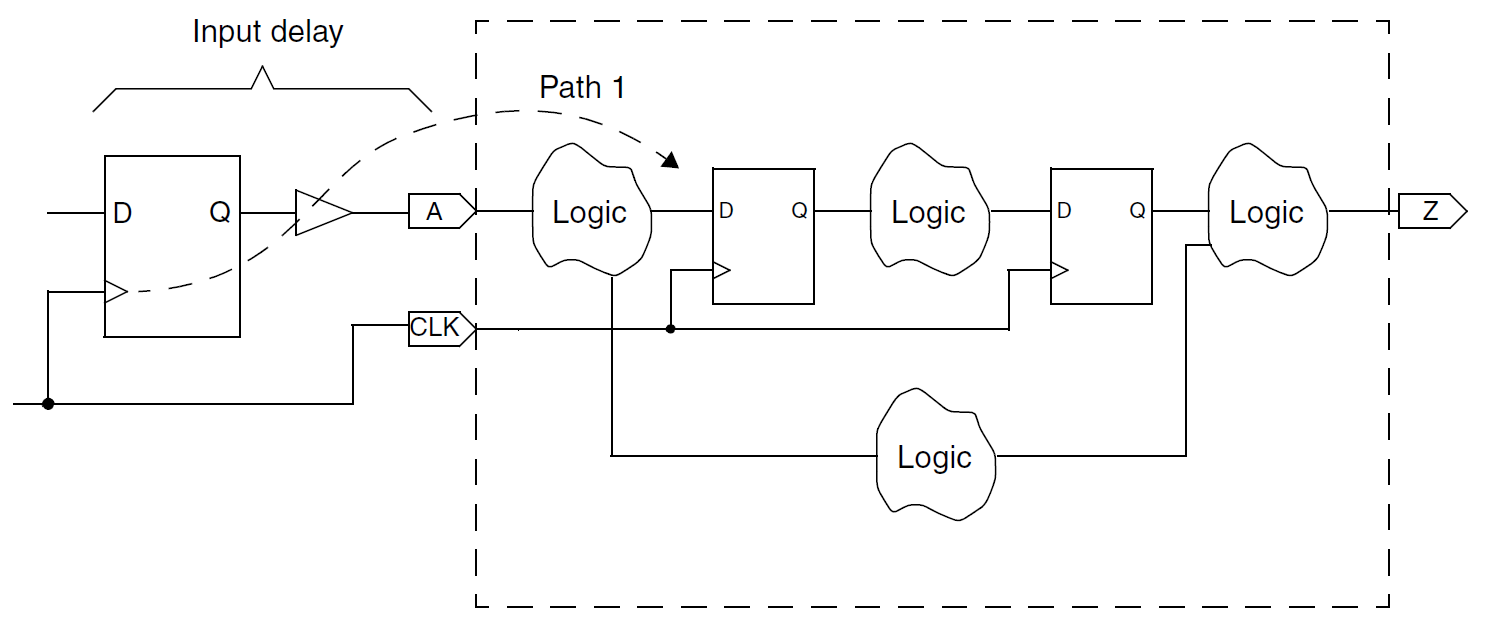

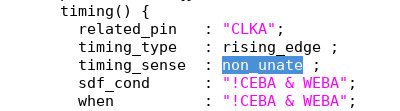

input pin的timing constraint如下图所示:

其含义为,当遇到CLKA上升沿时,

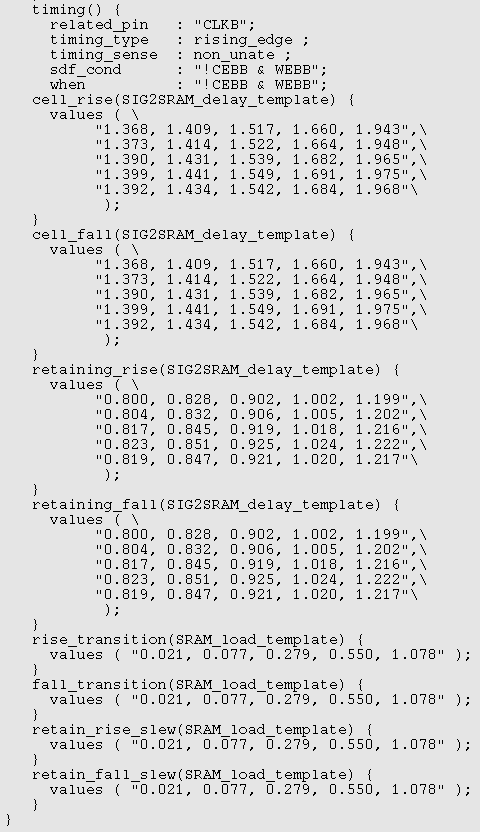

output pin constraint

这里input delay包含setup与hold两类timing check。以setup time check 0.099为例,信号变化需要至少在clock上升沿之前0.099ns。同理以hold time check 0.072为例,信号变化需要至少在clock上升沿之后0.072ns。

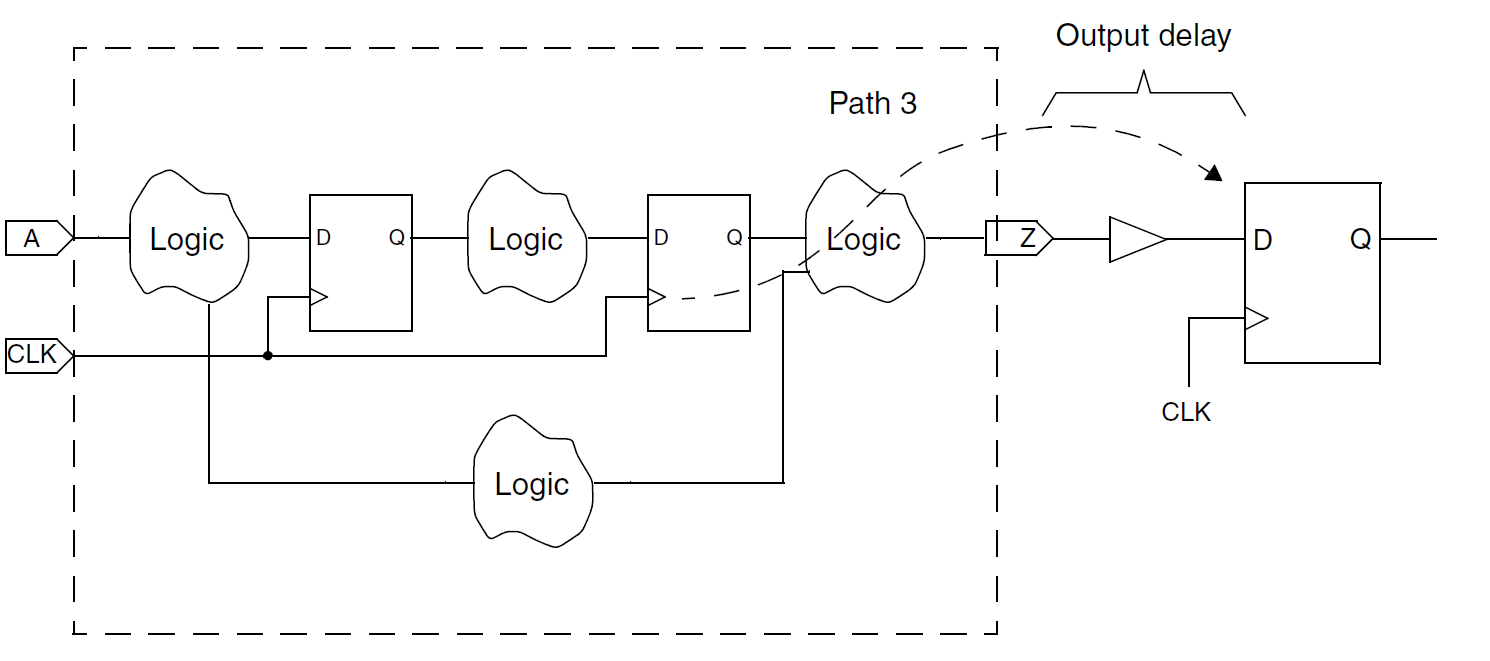

output delay的含义为

output delay设置需要包含路径延迟以及外部寄存器的setup time requirements。

什么是时序弧的unateness?

在编写.lib文件时,遇到timing_sense的条目。在TSMC SRAM的输出pin QA的定义中,timing_sense设置为non_unate,这是什么意思呢?

unateness主要用于回答这个问题:

如果input发生了变化(比如input置为1),该output会发生什么行为?(output置1?置0?还是保持原值?)

我们将output可能的行为分为以下三类:

- Positive Unate: Input置为1后,Output也置1或者保持。Input置为0后,Output也置0或者保持。E.g. Buffer, 与门,或门。

- Negative Unate: Input置为1后,Output置0或者保持。Input置为0后,Output置1或者保持。E.g. 非门。

- Non-Unate: Output的行为与input的行为无关。

对于SRAM的输出,Output取决于SRAM中储存的值,所以直接设置为non-unate即可。

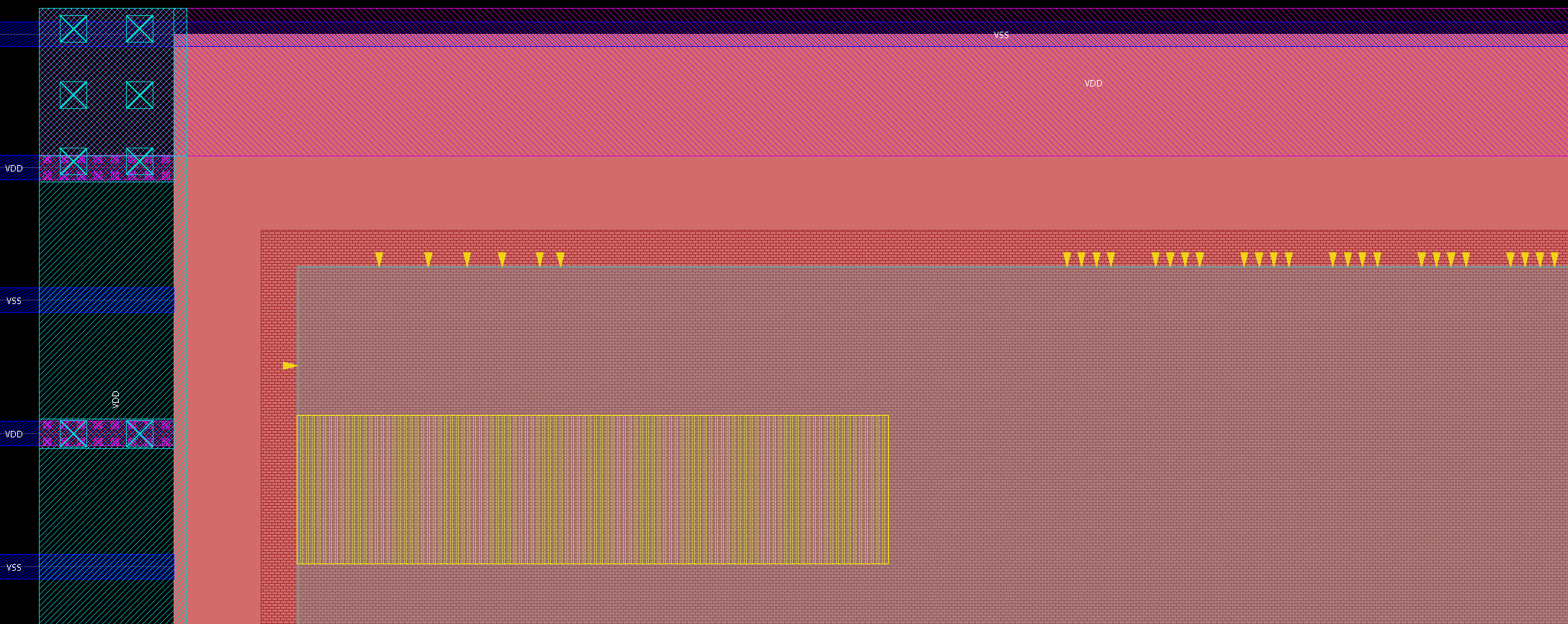

Merge GDS之后需要注意的点

为了防止merge之后有DRC rule的报错,现在将PR中各个阶段的check list记录如下:

Floorplan阶段,所有的hard macro和block需要打Halo,并在边界上打上针对性的RouteBlockage。所谓针对性的RouteBlockage即防止在hard macro的边界附近,外部走线与内部走线存在距离的问题。在我参与的第四次流片任务DigitalBridge芯片的设计中,我们的Compute-In-memory模块在边界上存在非常粗的M3与M4金属,而外部走线会忽略这些边界上金属的存在,从而使得在streamout之后,边界上的M3和M4走线报出大量DRC金属边界的错误。

打Stripe的时候,可以选择让stripe merge with ring,防止power stripe与power ring重叠之后,Via产生冲突。Powerplan结束后,尽量清理掉所有杂线,给后续routing留出空间的同时,也能避免很多潜在的DRC问题。

IO ring与core之间至少留出一定的距离(28nm HPC+工艺需至少留出25um的间距)

修复verify_drc后Metal_short的问题:

使用以下命令打印出所有metal short的net name1

dbget [dbget top.markers.subType Metal_short -p].objects.name

如果short_nets 列表中出现 0x0,说明有些 marker 没有关联到 net(或者说 dbget 查询到了空对象),这种情况在实际 DRC 中是可能的,比如 marker 和某些 vias、shapes关联但没 net。

可以在list中使用lsearch语句:1

set short_nets [lsearch -all -inline -not -exact $short_nets "0x0"]

完整的script如下:1

2

3

4

5

6

7set short_nets {}

foreach marker [dbget top.markers.subType Metal_short -p] {

foreach net [dbget $marker.objects.objects.name] {

lappend short_nets $net

}

}

set short_nets [lsort -unique $short_nets]

之后重新执行ecoRoute即可

Netlist Debuging

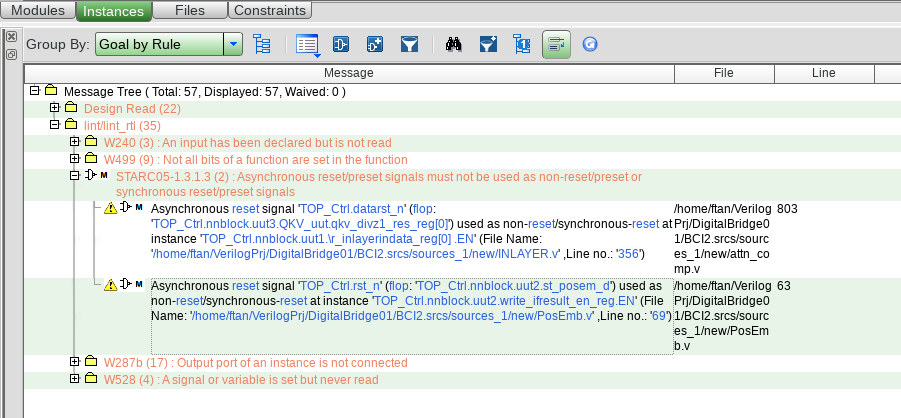

synthesis

混用同步reset和异步reset

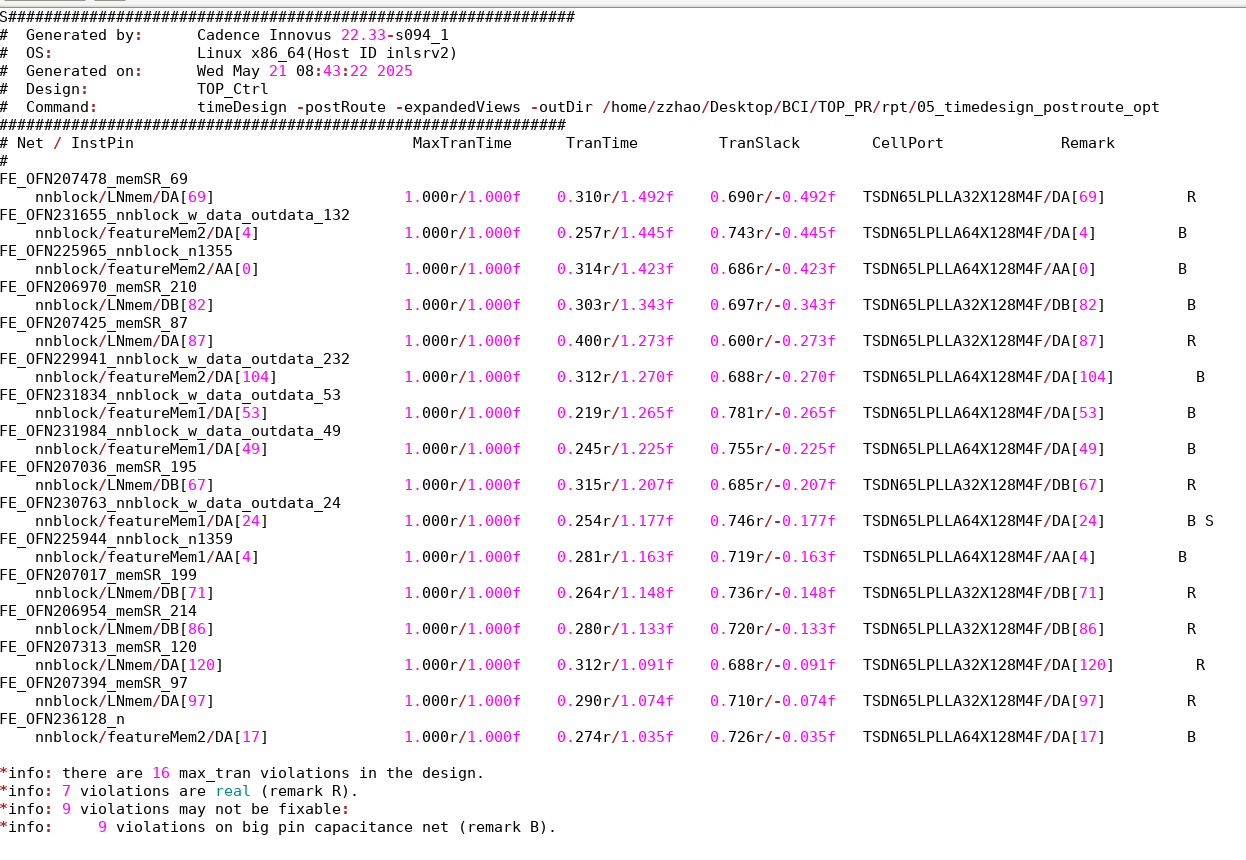

max transition

Digital as top中修复DRC需要注意的点

- Floorplan之后,检查CIM的边界,使用Halo或Routing Blockage规避潜在的金属间距造成的DRC错误。

- 在Floorplan和Powerplan的过程中,时常使用verify_drc命令进行检查,确保power stripe,power ring之间的via不存在drc问题。

检查GNC_rule,如果GNC_rule错误,在Virtuoso进行verilogIn会报奇怪的short问题。

LVS BOX

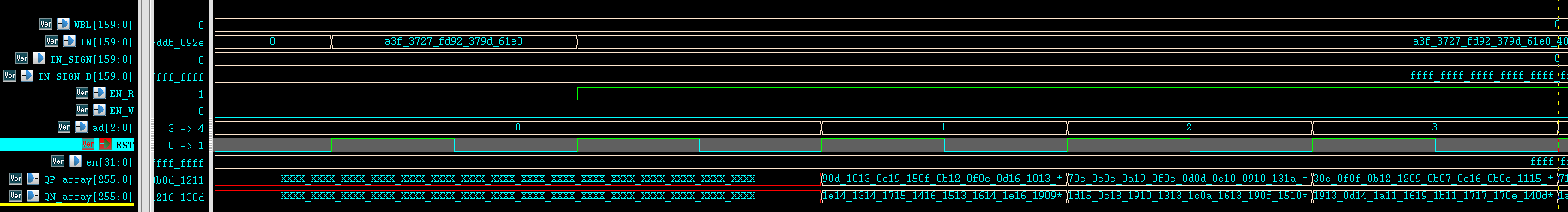

reference model时序不匹配的问题

在后仿的时候,定制的硬核部分可以使用reference model进行混仿。因为导入的