Twin-8T CIM Macro

Twin-8T CIM Macro

文章名:A Twin-8T SRAM Computation-in-Memory Unit-Macro for Multibit CNN-Based AI Edge Processors

这篇文章设计了一个基于电流的CIM Macro。提出了Twin-8T架构支持多比特输入(1,2,4)位。这些多bit的输入会被DAC转化为WL上不同的电平:VDDWL。而不同的VDDWL电平会在BL与BLB上产生不同的电流,这种架构面临的挑战是:当bit-level过多之后,bltline上的signal margin会降低。

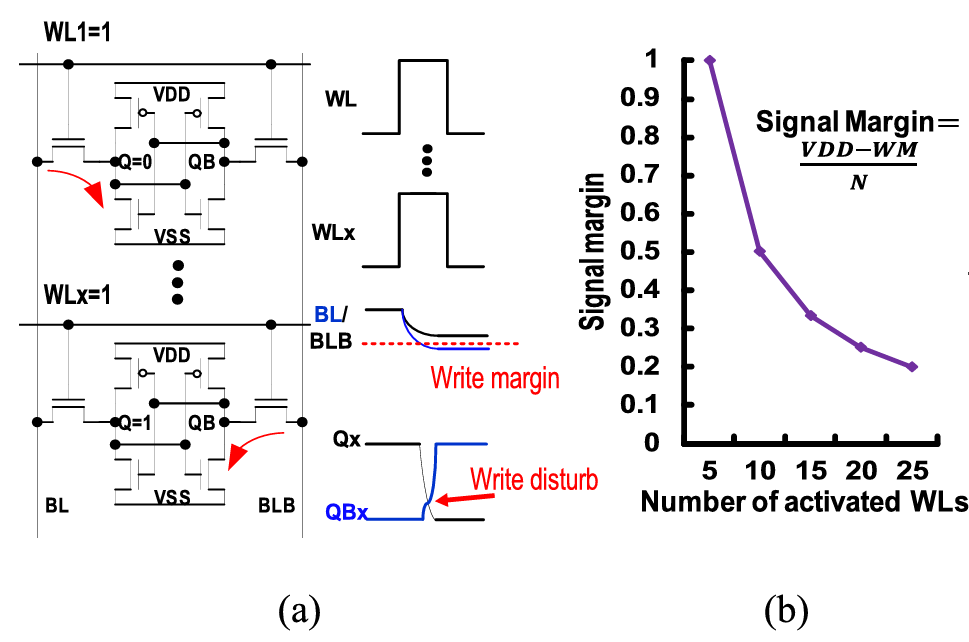

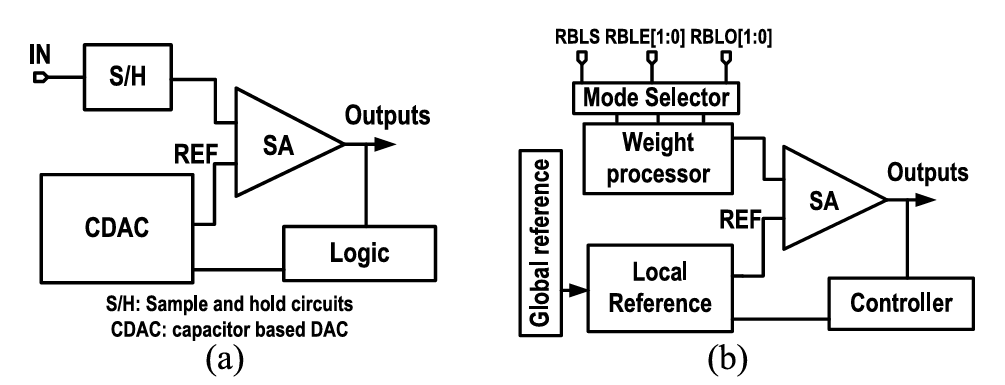

上图(a)是一个典型的基于电流的CIM架构,在预充电阶段,BL会被充电到一个固定的电压,每个SRAM cell输出的电流分成多个权重位。多个权重位的累加可能导致单个cell的贡献信号更小,当更多的电流组合存在之后,相邻结果之间的差距($ \Delta LSB $)就会变小。另外,bitline上的电压必须高于一个write-margin (WM) 的电压值,以防止过低的BL电压改写cell中已经存好的值 (write disturb)。

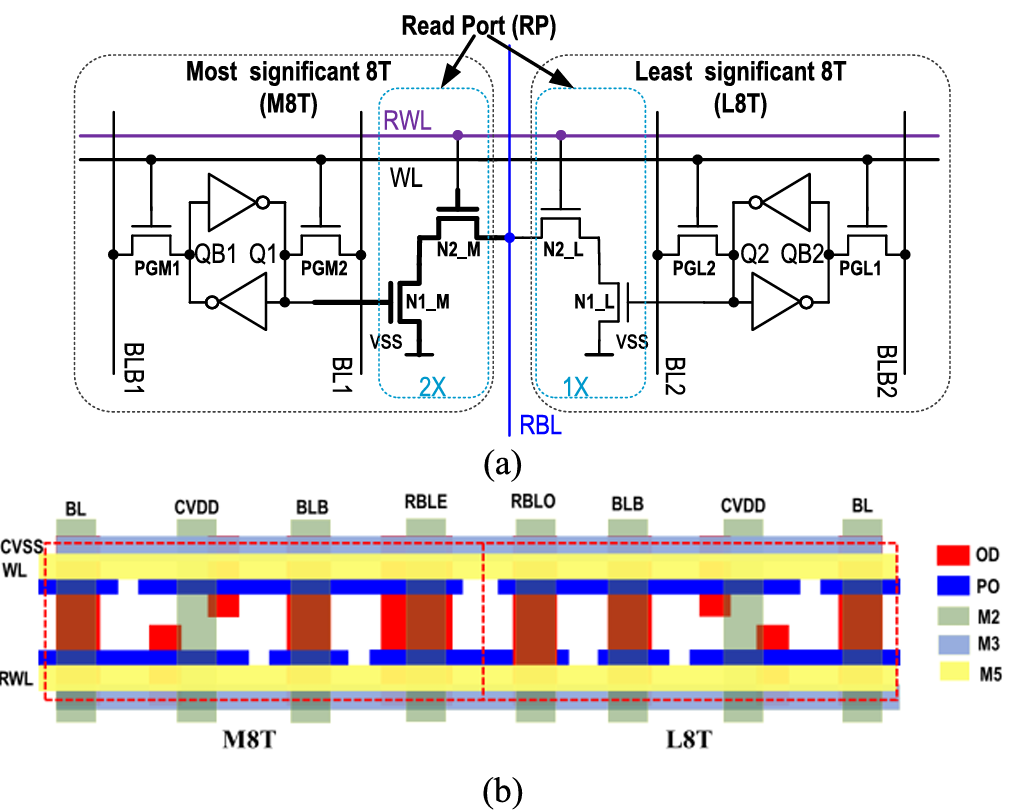

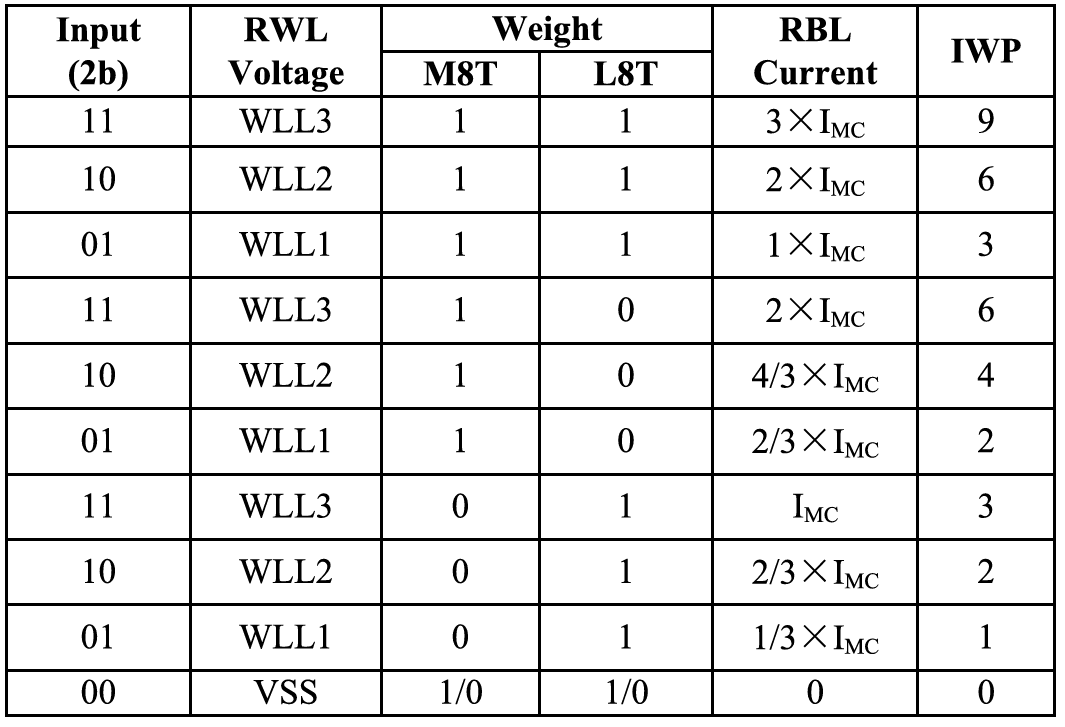

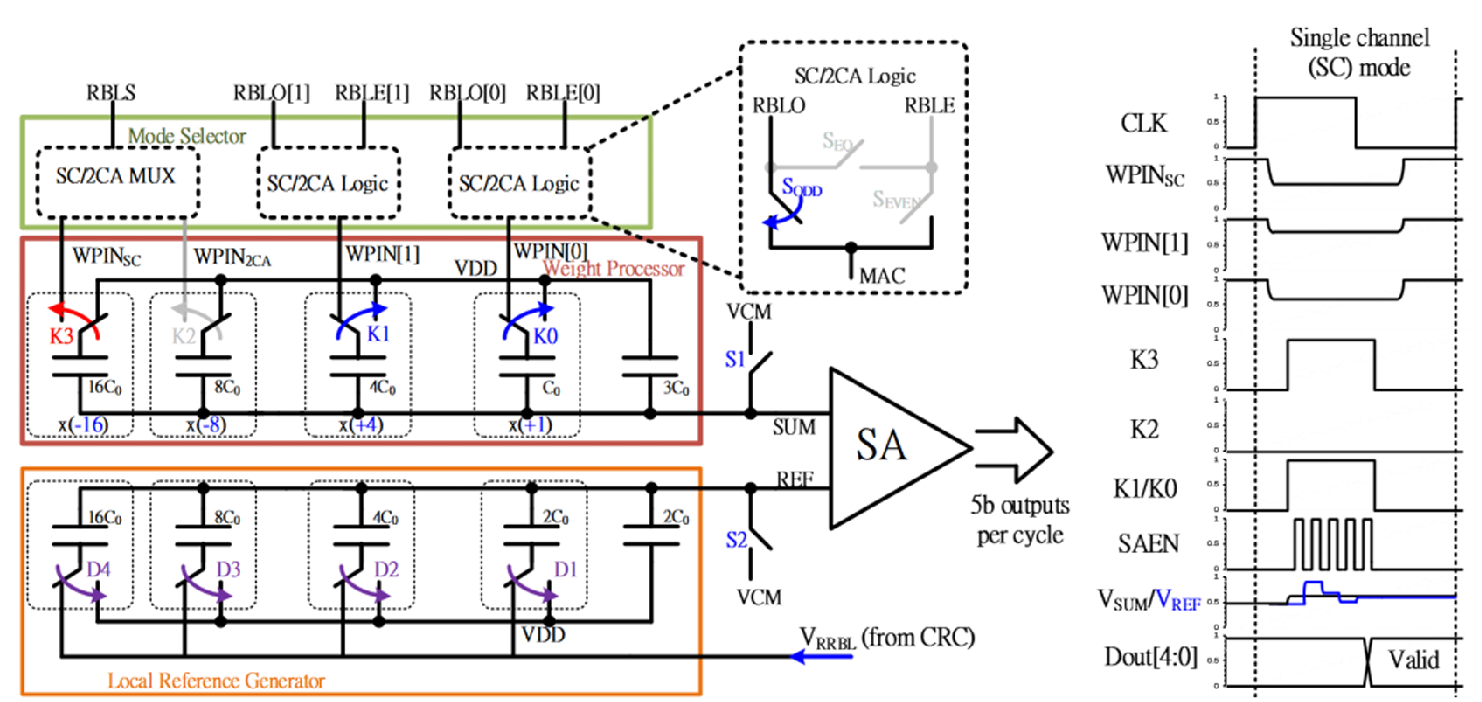

这个cell的创新点在于:把两个8T SRAM的RBL共享。左边的M8T的读出管宽度是右边L8T的两倍。这样左边8T cell对RBL的电流贡献就会是右边cell的两倍。当配置为2-bit-input乘以2-bit-weight的计算时,RWL上的电压将会有四种台阶。

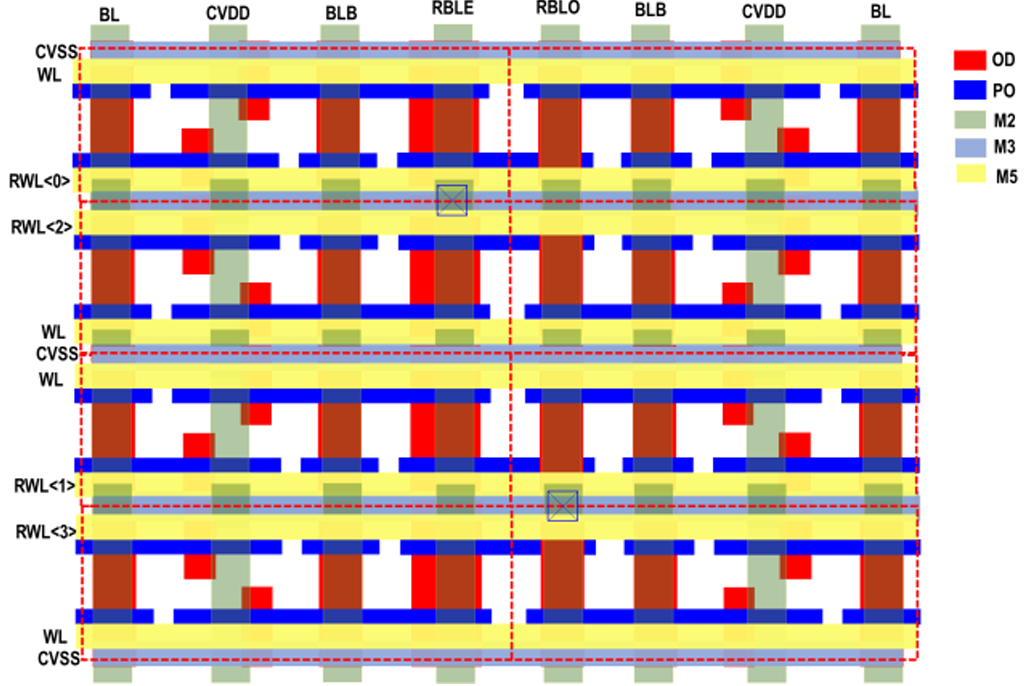

RBL分享节省出来的layout空间,该work将奇数行和偶数行的cell分为两组,一组挂在RBLE上,一组挂在RBLO上,用这种方式降低BL的parasitic load并提高signal margin。

对于读出电路,传统的ADC设计使用了固定的reference voltage,不支持可调性。而在这个设计里,ADC的reference用一个Local Reference Generator来根据不同的mode调整reference voltage。

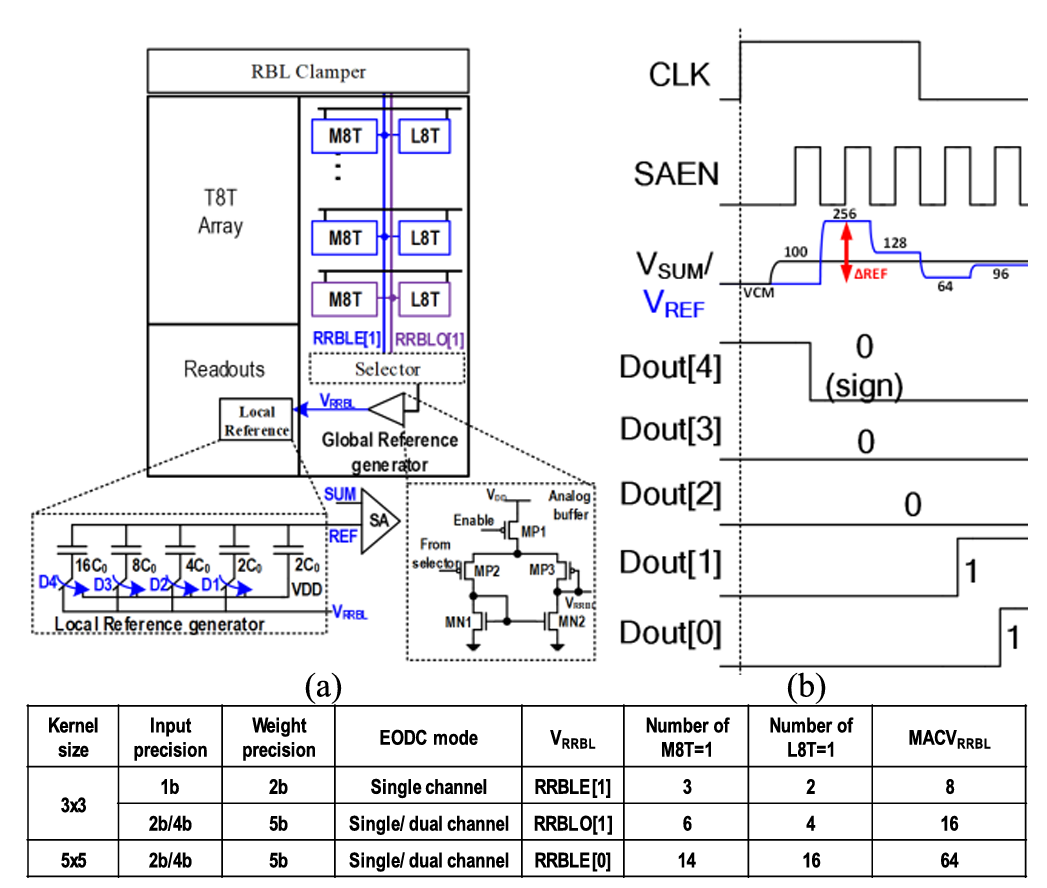

CGLRVG:Configurable global-local reference voltage generation

因为kernel size的不同,input和weight的bit精度也不一样。整个CIM macro分为以下的操作模式。

本文提出的Configurable Global & Local Reference Voltage Generation (CGLRVG) 由两部分组成,分别使global Reference Voltage Generator (GRVG)和Local Reference Voltage Generator (LRVG)。GRVG包含 Configurable Replica Columns (CRC) 和 Voltage Buffers (VB),在 CRC 中,Replica Read Bitline (RRBL) 通过设定数据模式,生成一个全局参考电压$V_{REF-G}$,它对应于目标MAC值所在的区间。对于一个 k-bit MACV(2’s complement 格式),MACV 的范围是:

举例以3×3 kernel、2-bit 输入、5-bit 权重为例,MACV的范围在-432到+405之间。输出精度量化到5bit,所以需要五个sensing phase。

GRVG:根据不同 CIM 配置(输入位宽、权重量化精度、kernel 大小等),灵活生成全局参考电压 $ V{REF-G}$ ,之后LRVG利用电容阵列和可控开关,把$ V{REF-G}$进行加权叠加或与VDD混合,从而生成多个局部参考电压$ V_{REF-L}$。

对于multi-bits CIM Macro的signal margin而言,当MACV较小时,PVT variation对signal margin影响较大。而当MACV较大时,RBL电压的波动对signal margin影响较大。